See Vivado™ Development Environment on amd.com

See Vivado™ Development Environment on amd.com

|

Version: Vivado 2020.2

Click to expand

In the multi-bank configuration, a maximum of three banks are supported by the Advanced I/O Wizard (AIOW). This design uses two banks with three XPHY NIBBLESLICEs from one XPIO bank and two XPHY NIBBLESLICEs from the other bank that transmit and receive data. The wizard requires the banks to be adjacent to each other. The transmit clock can be forwarded from the transmit core either via the clock forward pins or the transmit data pins from the bank. In this tutorial, the transmit clock is forwarded via the clock forward pins. The design uses the LVDS standard for the I/Os, and consequently, the data, transmit/capture clock, and PLL input clock use differential I/O pin pairs.

The wizard configures clocking circuitry using the XPLL that is needed to support these configurations. Refer to the Advanced I/O Wizard LogiCORE IP Product Guide (PG320) for more information on the AIOW. Each bank has a transmit clock of its own that the transmitter transmits. Similarly, the receiver receives a capture clock on each bank.

The VCK190 board provides fixed and variable clock sources for the Versal device and other function blocks. Refer to the VCK190 Evaluation Board User Guide (UG1366) to understand the clock generation and clock sources available on the board. This tutorial design uses the Programmable LPDDR4 SI570 Clock2 as a clock source to the clocking wizard. The clocking wizard receives the input clock from the on-board clock generator and provides its output clock from the CLKOUT1 port to the XPLL.CLKIN port of the TX and RX cores. CLKOUT1 is set to provide a clock of frequency 225 MHz when configuring the clocking wizard core clock_gen.

Clocking in the multi-bank source synchronous reference design is similar to the single-bank design. Instead of one instantiation of the XPLL as in the single-bank design, this design has two instantiations of the XPLLs, one for each bank. The TX and RX cores have two separate inputs for the PLL input clock, which is fed to the bank<0/1>_pll_clkin ports.

The reference design uses the PRBS generator and checker to exercise the I/Os. The design files for the PRBS generator and checker are provided in the design suite. The generator and checker are instantiated in the top-level file. The PRBS generator generates the data and feeds the TX core, which serializes it and transmits it to the RX core via an external loopback cable/card. This tutorial uses the FMC XM107 loopback card. The RX core feeds the data to the PRBS checker after deserializing it. The checker flags an error if it detects any mismatch. The block diagram of the reference design is shown in the following figure. The transmit clock is generated by feeding a 01010101 pattern to the corresponding clock forwarding pins on each bank.

Click to expand

The following steps describe how to configure and set up the project before building the TX and RX cores using the AIOW.

-

Clone the tutorial to get all the source files.

-

Create a separate directory named Versal_ssync_rxtx_intrfce_mb to build the new project.

-

Launch the Vivado tools 2020.2 or later from the newly created directory.

-

Under Quick Start, select Create Project.

-

Click Next for the prompt to Create a New Vivado Project and use Versal_ssync_rxtx_intrfce_mb for the name of the project. Deselect Create a project subdirectory.

-

Click Next. For Project Type, select RTL project. Deselect Do not specify sources at this time.

-

Add the source files from the Design folder under the Multi_bank_source_synchronous_design folder.

-

Add the files toplevel_mb.sv, Prbs_Any.vhd, and Prbs_RxTx.vhd. Make sure the library is set to xil_defaultlib, and the files are used for synthesis and simulation by setting it under the HDL Source For column.

-

Similarly, add the file toplevel_testbench_mb.sv and toplevel_sim_mb.sv from the Simulation folder under the Multi_bank_source_synchronous_design folder. Make sure the Library is set to xil_defaultlib and the file is used only for simulation by setting it under the HDL Sources For column.

-

Select Scan and add RTL include files into project and Copy sources into project. Set the Target Language to Verilog and the Simulator Language to Mixed.

-

Click Next to proceed to adding the constraint files.

-

Add the file toplevel_mb.xdc from the Constraints folder under the multi_bank_source_synchronous_design folder. Select Copy constraints files into project.

-

Click Next to select the part for the project. Select part xcvc1902-vsva2197-2MP-e-S for the reference designs and click Next.

-

On the summary page for the project, make sure all the details match the settings and then click Finish.

-

The Vivado tools should create a project and display the hierarchy of the files under the Sources folder.

Click to expand

The VCK190 board has an I2C programmable SI570 low-jitter 3.3V LVDS differential oscillator (U3) connected to the GC inputs of U1 LPDDR4_2 interface bank 705. The LPDDR4_CLK2_P and LPDDR4_CLK2_N series capacitor coupled clock signals are connected to XCVC1902 Adaptive SoC U1 pins AW27 and AY27, respectively. At power-up, this clock defaults to an output frequency of 200.000 MHz. User applications or the System Controller can change the output frequency within the range of 10 MHz to 945 MHz through the I2C bus interface. Power cycling the VCK190 board reverts this user clock to the default frequency of 200.000 MHz. This design uses the onboard oscillator to provide PLL clock inputs to the Clocking Wizard. This core generated using the clocking wizard in turn provides its output clock (set to 225 MHz) on port CLKOUT1 to the Advanced I/O Wizard TX (Bank 706) and Advanced I/O Wizard RX (Bank 707) cores. The bank0_pll_clkin and bank1_pll_clkin ports of these TX and RX cores is driven by this CLKOUT1, which acts as the PLL input clocks to these cores.

Follow the steps below to generate the core that will provide the PLL input clock to the TX and RX cores. See the figures in this section for reference:

-

To start generating this core, open the IP catalog and search for Clocking Wizard. Double-click Clocking Wizard from the catalog to open the Customize IP window.

-

For Component Name, enter clock_gen, which is used in the reference design.

Note: The component name should match the module name used in the top-level design.

-

Under the Clocking Features Tab, for the clocking primitive select MMCM.

-

On the same tab, set the input clock information as shown in the figure:

a. Input Clock: Primary

b. Port Name: clk in1

c. Input Frequency(MHz): 200

d. PLL Input Clock Frequency: 200 (This is important because the on-board clock defaults to 200MHz,)

e. Source: Differential clock capable pin

-

In the Output Clocks tab, set the following:

a. Output Clock: clk_out1

b. Port Name: clk_out1

c. Output Freq (MHz) Requested: 225

d. Phase (Degrees) Requested: 0.000

e. Duty Cycle (%) Requested: 50.000

f. Drives: BUFG

g. Clock Grouping: Auto

-

In the MMCM Settings Tab, set the following:

a. Check the Allow Override Mode box

b. Bandwidth: Low.

c. CLKFBOUT_MULT: 18.

d. CLKFBOUT_PHASE: 0.

e. COMPENSATION: AUTO

f. DIVCLK_DIVIDE: 1

g. CLKOUTFB_PHASE_CTRL: None

h. In the second table, set Divide: 16

i. Duty Cycle: 0.500

j. Phase: 0.000

Refer to the Versal Adaptive SoC Clocking Resources Architectural Manual (AM003) to understand how Fvco and Fclkout is calculated. Also, refer to the Versal AI Core Series Data Sheet (DS957) to follow the limits for Fvco.

Fvco = Fclkin × M/D

Fclkout = Fclkin × M/(D*O)

Where M is CLKFBOUT_MULT, D is DIVCLK_DIVIDE, and O is Divide from the values set previously. In this tutorial design, Fclkin = 200 MHz. Thus, Fvco = 3600 MHz and Fclkout = 225 MHz.

- The summary tab should look as shown in the following figure.

- Click OK after reviewing the settings. The IP is now customized and the Generate the Output Products prompt appears. Set the Synthesis Option to Out of context per IP and then click Generate to launch the design run for the newly generated core.

Click to expand

In this source synchronous design, the capture clock is the same as the transmit clock, which is looped back externally via a loopback card on the board from the TX to the RX core. The transmit clock is forwarded with the data by the TX core. The clock-to-data relation in this design is edge aligned and is shown in the following figure. The XPLL in the RX core needs a PLL input clock apart from the capture clock received with the data. This PLL input clock acts as the input to the XPLL (CLKIN port of the XPLL). Because this is a multi-bank design (two banks), the wizard instantiates two instances of the XPLLs, one for each bank. Consequently, the PLL input clock is received on the bank<0/1>_pll_clkin ports of the RX core instantiated by the wizard. CLKOUT1 of clock_gen is used to provide this input PLL clock. This clock received on the bank<0/1>_pll_clkin ports is fed to the XPLL instantiations in the design.

The capture clock should be received on the package pin pair assigned in the constraints file. It should be received on NIBBLESLICE[0] because it is the only NIBBLESLICE that has clock forwarding abilities. Refer to the "Inter-nibble and Inter-byte Clocking Within an XPIO Bank" figure in the Versal Adaptive SoC SelectIO Resources Architecture Manual (AM010).

The data received at the RX core interface is transmitted to the programmable logic via the PHY and the bank instances, where it gets checked by the PRBS checker.

After following the previous steps to generate the top-level design and the clock source core, the next step is to generate TX and RX cores for operation. Follow these steps to generate the RX core using the AIOW. See the figures in this section for reference.

-

To start generating a core for the RX, open the IP catalog and search for Advanced I/O Wizard. Double-click Advanced I/O Wizard from the catalog to open the Customize IP window.

-

For Component Name, enter Rx_2bank_ssync_intrfce, which is used in the reference design.

Note: The component name should match the module name used in the top-level design.

-

In the Basic Tab, set Application to SOURCE SYNCHRONOUS from the drop-down list. Set Bus Direction to RX ONLY.

-

On the same tab, set the following:

a. Interface Speed: 1800 Mb/s

b. PLL Clock Source: Fabric(Driven by BUFG)

c. PLL Input Clock Frequency: 225

d. Clock Data Relation: Edge DDR

e. RX Serialization Factor: 8

f. Select Include PLL in Core

g. The remaining options can be set to the default.

-

In the Advanced tab, set the following:

a. Select REDUCE CONTROL SIGNALS and Enable BLI logic. When BLI logic is enabled, the BLI registers between fabric and XPHY can be used to help with timing closure.

b. Differential I/O Std: LVDS15.

c. Number of Banks: 2 (because this is a multi-bank design).

-

In the Pin Configuration tab, make two entries in the table. One entry is for the data and strobe for bank0. The other entry is for the data and strobe for bank1.

-

Data and Strobe Setting #1

- Pin Direction = RX

- I/O Type = Differential

- Signal Type = Data

- Strobe I/O Type = Differential

- Strobe Name = strobe_b0

- Signal Name = Rx_data_b0

- Number of Data Channels = 4

-

Data and Strobe Setting #2

- Pin Direction = RX

- I/O Type = Differential

- Signal Type = Data

- Strobe I/O Type = Differential

- Strobe Name = strobe_b1

- Signal Name = Rx_data_b1

- Number of Data Channels = 2

- Check the Summary tab. It should show 12 RX pins enabled and 4 strobe pins enabled.

- Click OK after reviewing the settings. The IP is now customized, and the Generate the Output Products prompt appears. Set the Synthesis Option to Out of context per IP and click Generate to launch the design run for the newly generated RX core. The default placement might look different, but this does not matter because the default placement is adjusted later based on the pin locations in the constraints file.

This RX core is set up to work for a data rate of 1800 Mb/s. Also, the core is configured for LVDS15 in the reference design. This multi-bank design is configured for an edge-aligned DDR system. An XPIO bank has 54 pins. The design uses ten pins for bank 0 instance in the form of eight pins for data and two pins for capture clock (four pairs for data and one pair for capture clock). The other instance of the bank uses six pins in the form of four pins for data and two pins for capture clock (two pairs for data and one pair for capture clock). The wizard allocates one XPLL per bank. The design constrains the ports for the receive interfaces, and the wizard takes care of the placement.

Click to expand

In the reference design, the TX core sends out the strobe or the transmit clock along with the data. The data in this design is generated using the PRBS generator. The strobe is generated by feeding the pattern 01010101 to the NIBBLESLICEs forwarding the strobe. The data generated by the PRBS generator is fed into the TX core from the programmable logic, which follows the TX datapath through a serializer and output delay. The serializer supports 8:1, 4:1, and 2:1 serialization. This design uses 8:1 serialization. The data is transmitted through the TX data pins of the core. To understand the data flow operation inside the TX core, refer to the Versal Adaptive SoC SelectIO Resources Architecture Manual (AM010).

The TX core needs a PLL input clock that acts as the input to the XPLL (CLKIN port of the XPLL). The PLL input clock from the CLKOUT1 port of the clock_gen core is received on the bank0_pll_clkin and bank1_pll_clkin ports of the TX core, which is passed to the XPLLs instantiated in the core for both the banks. The transmit clock can be forwarded either through the data pins or clock forwarding pins on the TX core. The transmit clock should be transmitted on NIBBLESLICE[0] for it to be forwarded to the RX core. This design uses the clock forwarding pins to forward the transmit clock. A clock pattern of 01010101 is fed to the clock forwarding pins. This results in the same output clock.

Follow these steps to generate the TX core using the AIOW. See the figures in this section for reference.

-

To start generating a core for the TX, open the IP catalog and search for Advanced I/O Wizard. Double-click Advanced I/O Wizard to open the Customize IP window for the wizard.

-

For Component Name, enter Tx_2bank_ssync_intrfce, which is used in the reference design.

Note: The component name should match the module name used in the top-level design.

-

In the Basic Tab, set Application to SOURCE SYNCHRONOUS from the drop-down list, and set Bus Direction to TX ONLY.

-

On the same tab, set the following:

a. Interface Speed: 1800 Mb/s.

b. PLL Clock Source: Fabric (Driven by BUFG).

c. PLL Input Clock Frequency: 225.

d. Forwarded Clock Phase to 0.

e. Clock Data Relation: Edge DDR.

f. TX Serialization Factor: 8

g. Select Include PLL in Core.

h. The remaining options can be set to the default.

-

In the Advanced tab, set the following:

a. Select REDUCE CONTROL SIGNALS and Enable BLI logic. When BLI logic is enabled, the BLI registers between fabric and XPHY can be used to help with timing closure.

b. Differential I/O Std: LVDS15

c. Number of Banks: 2 (because this is a multi-bank design).

- In the Pin Configuration tab, add four entries in the table. There are two entries per bank. The data and the clock forwarding pins are entered separately in the table for each bank. Tx_data_b0 and Clk_fwd_b0 list the pin configuration for the first bank instance, and similarly, Tx_data_b1 and Clk_fwd_b1 list the pin configuration for the second bank instance.

-

Data Setting #1

- Pin Direction = TX

- I/O Type = Differential

- Signal Type = Data

- Signal Name = Tx_data_b0

- Number of Data Channels = 4

-

Data Setting #2

- Pin Direction = TX

- I/O Type = Differential

- Signal Type = Clk Fwd

- Signal Name = Clk_fwd_b0

- Number of Data Channels = 1

-

Data Setting #3

- Pin Direction = TX

- I/O Type = Differential

- Signal Type = Data

- Signal Name = Tx_data_b1

- Number of Data Channels = 2

-

Data Setting #4

- Pin Direction = TX

- I/O Type = Differential

- Signal Type = Clk Fwd

- Signal Name = Clk_fwd_b1

- Number of Data Channels = 1

- Check the Summary tab. It should show 16 TX pins enabled: four pairs of data pins with one pair of clock forwarding pins for bank instance 0 and two pairs of data pins with one pair of clock forwarding pins for bank instance 1.

- Click OK after reviewing the settings. The IP is now customized and the Generate the Output Products prompt appears. Set the Synthesis Option to Out of context per IP and click Generate to launch the design run for the newly generated TX core. The default placement might look different, but this does not matter because the default placement is adjusted later based on the pin locations in the constraints file.

This TX core is set up for a data rate of 1800 Mb/s. Also, the core is configured and tested for LVDS15 in this reference design. This design uses the clock from the CLKOUT1 port of the clock_gen core to feed the XPLLs of the TX core. This PLL input clock (CLKOUT1 from clock_gen) is driven through the BUFG and then passed to the XPLLs in the TX core through a bank<0/1>_pll_clkin port within each bank. An XPIO bank has 54 pins, and the design uses 16 pins in the form of six pairs of data pins and one pair of strobe pins for each of the two bank instances. The design constrains the ports for the transmit interfaces, and the wizard takes care of the placement.

Click to expand

Virtual Input/Output with AXIS Interface (VIO) is a customizable core that can monitor and drive internal FPGA signals in real time. This design uses VIO in order to drive control signals such as resets. Follow the steps below to add and configure VIO:

-

To start generating a VIO core, open the IP catalog and search for VIO. Double-click on the IP from the catalog to open the Customize IP window.

-

For Component Name, enter vio_0, which is used in the reference design.

Note: The component name should match the module name used in the top-level design.

- Set Input Probe Count to 15 and Output Probe Count to 12.

- Click OK after reviewing the settings. The IP is now customized and the Generate the Output Products prompt appears. Set the Synthesis Option to Out of context per IP and click Generate to launch the design run for the newly generated VIO core.

Click to expand

Integrated Logic Analyzer with AXIS Interface (ILA) is a customizable logic analyzer core that can be used to monitor the internal signals of a design. This design uses ILA in order to monitor internal signals of the design such as ready, pll_locked, and error signals. Follow the steps below to add and configure ILA:

-

To start generating an ILA core, open the IP catalog and search for ILA. Double-click on the IP from the catalog to open the Customize IP window.

-

For Component Name, enter ila_0, which is used in the reference design.

Note: The component name should match the module name used in the top-level design.

- Set Number of Probes to 19.

- Change the width of probe ports probe11 through probe18 to 8. The rest of the ports should have width 1.

- Click OK after reviewing the settings. The IP is now customized and the Generate the Output Products prompt appears. Set the Synthesis Option to Out of context per IP and then click Generate to launch the design run for the newly generated ILA core.

Click to expand

In order to generate the PDI for a Versal device, the design needs to be built with the Control, Interfaces, and Processing Systems (CIPS) IP. The CIPS IP is the software interface around the Versal processing system. The Versal family consists of a system-on-chip (SoC) style integrated processing system (PS) and a programmable logic (PL) unit, NoC, and AI Engine providing an extensible and flexible SoC solution on a single die. In the Versal Adaptive SoC architecture, the ILA and VIO IPs require a debug hub IP in order to function. This debug hub IP must in turn be connected to the CIPS processor. A few additional blocks provide necessary clocking, reset, and NOC connectivity required for the debug IP to operate correctly.

Follow the steps below to create the Block Design:

-

Under Flow Navigator, click on Create Block Design. Name it design_1.

-

Press the '+' button to add IP. Search for CIPS in the search box and press ENTER. Double click the CIPS IP to customize the IP.

- Under Configuration Options, navigate to PS-PMC > Clock Configuration. Go to Output Clocks > PMC Domain Clocks > PL Fabric Clocks and select PL0_REF_CLK as shown in the figure.

- Under Configuration Options, navigate to PS-PMC > PL-PS Interfaces. Set Number of PL Resets to 1 as shown in the figure.

- Under Configuration Options, navigate to PS-PMC > NoC. Under Non Coherent Interfaces, set PMC to NoC.

- Click OK.

-

Press the '+' button to add IP. Search for Clocking Wizard in the search box and press ENTER.

-

Press the '+' button to add IP. Search for Processor System Reset in the search box and press ENTER.

-

Press the '+' button to add IP. Search for AXI NoC in the search box and press ENTER. Double click the AXI NoC IP to customize the IP.

- On the General tab, set Number of AXI Clocks to 2.

- Under Inputs > AXI Inputs, make the changes as shown in the following figure.

- Under Outputs > AXI Outputs, make the changes as shown in the following figure.

- Click OK.

-

Press the '+' button to add IP. Search for AXI4 Debug Hub in the search box and press ENTER.

-

Make the connections manually by connecting the ports as shown in the figure. To connect the ports drag the pencil marker from the source port to the destination port.

-

Click on Validate Design under the Tools option on the top bar.

-

In the Address Editor tab, right click the object and select Assign.

- Save the Block Design and close it. Right click the block design "design_1" under Sources and select Generate Output Products. Select Out of context per Block Design when prompted to select the Synthesis Option.

Click to expand

The top-level design file (toplevel_mb.sv) includes the toplevel_mb module. This module helps connect the interfaces such as clocks, debug ports, and I/O ports with the appropriate sources. The top-level design houses the instantiation of both the RX and the TX cores. To test the design, the PRBS patterns from the custom PRBS generator provided in the design suite can be used to generate and check the received data.

The PRBS generator generates the 8-bit data for each pair and feeds it to the TX core, which in turn transmits it through the TX pins. The PRBS generator also houses an error injecting mechanism. The data is received on the I/O ports of the RX core through external loopback. The RX core forwards the deserialized data through the PHY to the programmable logic. This deserialized data is then fed into the PRBS checker to check for any failures.

The top-level design files include two constraints files. The toplevel_mb.xdc file is used to create clocks for the design and assign a location to all the I/O ports in the design. The reference design constrains the design to optimally support high data rates. The toplevel_mb.xdc file is used to assign locations or pins to all the I/O ports in the design, and set attributes if needed. The user must constrain the TX and RX ports. The Vivado tools can assign the XPHY nibbles to the XPHY sites. The Advanced I/O Planner should be used to help with pin assignments (see Advanced I/O Wizard LogiCORE IP Product Guide (PG320)) when using the AIOW. This tutorial uses prebuilt hardware in the form of the external loopback card. Thus, the I/O locations are provided in the XDC file.

Click to expand

This design uses the FMC XM107 Loopback Card. This card provides hard-wired loopback connections. Thirty-four sets of differential pair nets LA[00:16]_P/N are looped one-to-one to LA[17:33]_P/N. These loops are direct-connect. Refer to the FMC XM107 Loopback Card User Guide (UG539). Following is the table from the FMC XM107 Loopback Card User Guide which highlights the loopback connections on the card. The XM107 loopback card goes on connector J51 on the VCK190 platform for this design.

This design has been tested with a xcvc1902-vsva2197-2MP-e-S Versal device. In the reference design, bank 706 and bank 707 are interchangeably used as TX and RX cores to transmit and receive data. Bank instance 0 for the TX is on bank 706 while bank instance 0 for the RX is on bank 707. Similarly, bank instance 1 for the TX is on bank 707 while bank instance 1 for the RX is on bank 706. Refer to the VCK190 schematics (XTP610). The pin assignments mentioned in the constraints file (toplevel_mb.xdc) take care of these available loopback connections. The transmit clock for bank instance 0 is sent on BD23 and BD24, which loops back as the capture clock on BB16 and BC16. The transmit clock for bank instance 1 is sent on BE17 and BD17 which loops back as the capture clock on BC23 and BD22.

At this point all the files are added to the project, and both the RX and TX cores are generated. The design is ready to be synthesized and implemented. After the design has been implemented without any errors, build the device image to generate a PDI to run on the hardware.

Before programming the PDI, make sure the power rail VADJ_FMC shows a reading of 1.5V. This ensures that the FMC card is operational. DS26 is the status LED on the board for VADJ_FMC. If VADJ_FMC is not set to the correct value, or the DS26 status LED is not green, follow the workaround below. Download the VCK190 Software Install and Board Setup Tutorial (XTP619) and VCK190 Board Interface Test (BIT) Tutorial (XTP613). Install the UART drivers by following the "UART Driver Install" section in the VCK190 Software Install and Board Setup Tutorial (XTP619). Make sure to follow the appropriate steps under "Hardware Setup." The baud rate needs to be set to 115200, otherwise, the COM port displays all garbled characters. Follow the steps under "Terminal Setup." This tutorial was tested using the USB-C cable (JTAG Boot mode). Make sure this cable is the only one connected to the desktop being used. After the system controller firmware boots up on the appropriate COM port, use the command: nohup /usr/bin/boardframework.sh.

After the COM port displays DONE, close the COM Port. At this time all the COM Ports should be closed. Follow the steps under "VCK190 Board Interface Test Setup." Navigate to the directory which has the executable BoardUI.exe.

Launch BoardUI.exe and click OK.

Click on Layout and deselect Hide Right Pane, then click on the System Controller tab in the bottom section.

Click on FMC and under Set VADJ and Current, enter 1.5 in the box beside Set VADJ as shown in the following figure. Click on the Set VADJ button.

If there are no errors, click on Get VADJ. It should display 1.5V.

These steps should ensure that the VADJ_FMC power rail is set to the correct value. This workaround is needed each time the board is power-cycled. This workaround might not be needed in future versions of the System Controller firmware.

After VADJ_FMC is correctly set, use the Hardware Manager from the Vivado tools to program the PDI and the probes file (.ltx). Upon programming, the VIO window appears, through which you can set the necessary resets to all the cores and the error injections for PRBS Generator and Checker. The ILA window can be used to check the status signals and the data. To reset the board using the VIO output signals, follow the sequence below:

- Set int_prbs_gen_rst_b0 to 1

- Set int_prbs_gen_rst_b1 to 1

- Set int_prbs_chk_rst_b0 to 1

- Set int_prbs_chk_rst_b1 to 1

- Set int_rx_rst to 1

- Set int_pll_rst_pll_rx_b0 to 1

- Set int_pll_rst_pll_rx_b1 to 1

- Set int_tx_rst to 1

- Set int_pll_rst_pll_tx_b0 to 1

- Set int_pll_rst_pll_tx_b1 to 1

This should clear all the pll_locked, intf_rdy, and PRBS gen/chk signals. To set all the status signals again, release the resets by following the sequence below:

- Set int_pll_rst_pll_tx_b0 to 0

- Set int_pll_rst_pll_tx_b1 to 0

- Set int_tx_rst to 0

- Set int_pll_rst_pll_rx_b1 to 0

- Set int_pll_rst_pll_rx_b0 to 0

- Set int_rx_rst to 0

- Set int_prbs_chk_rst_b1 to 0

- Set int_prbs_chk_rst_b0 to 0

- Set int_prbs_gen_rst_b1 to 0

- Set int_prbs_gen_rst_b0 to 0

This should release all the resets, and the design is operational. In order to inject the error, set int_inject_err_b0 and int_inject_err_b1 to 1. This should set the error flag, int_prbs_err_all_sync, int_prbs_err00_b0_sync, and int_prbs_err00_b1_sync. Alternatively, use the script reset_mb.tcl on the TCL console.

Click to expand

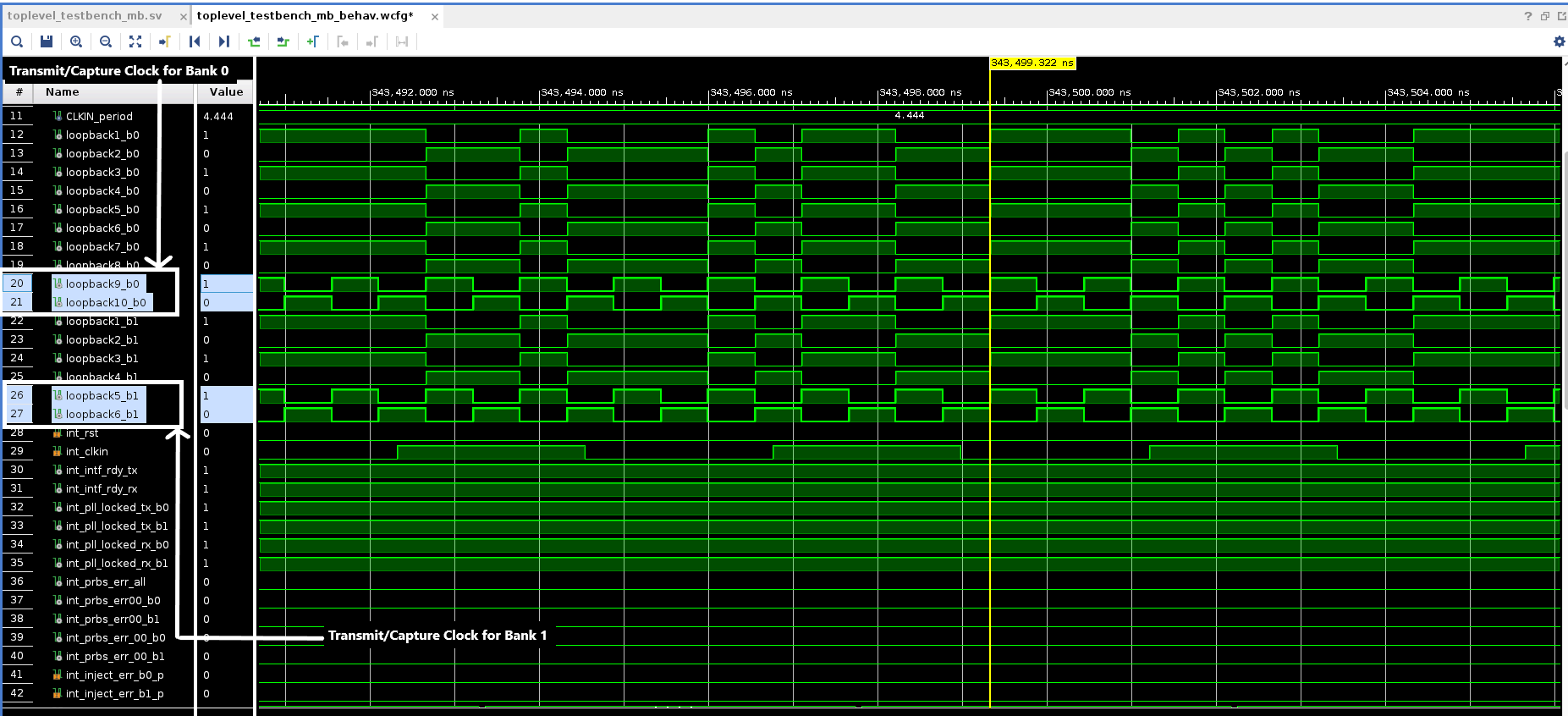

The design uses the toplevel_testbench_mb.sv file to create a simple test bench. This test bench connects the TX core to the RX core via loopback_b<0/1> connections (wires). The transmit clock is transmitted on loopback9_b0 and loopback10_b0 loopback wires for instance 0, whereas for instance 1, it is transmitted on loopback5_b1 and loopback6_b1. All the other loopback connections are used to transmit and receive the data. The clock-to-data relationship is edge aligned as shown in the following figure captured from the simulation.

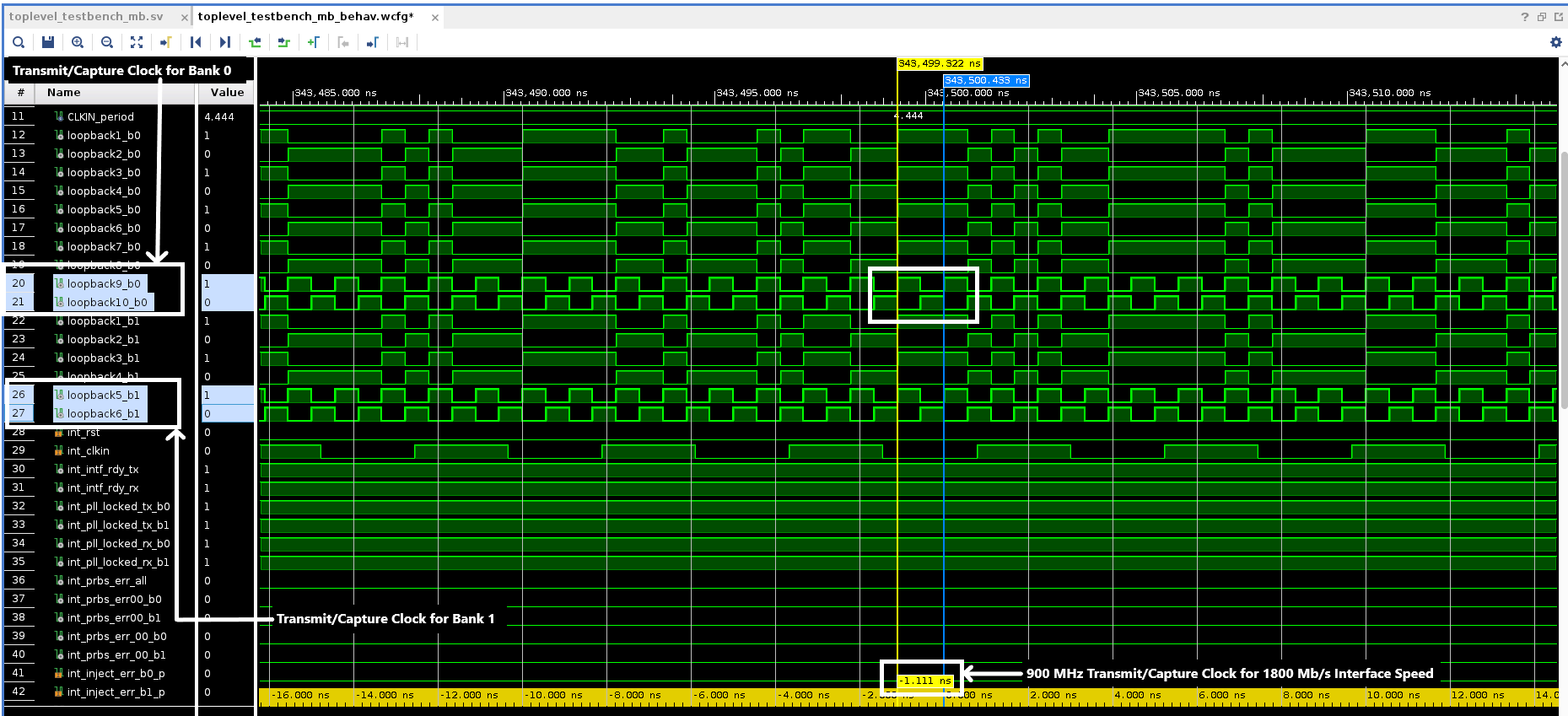

The test bench provides the necessary clock and resets to the design, and triggers its operation. The PLL input clock is provided at 4.444 ns (225 MHz) to the RX and TX cores. The transmit/capture clock toggles at 900 Mb/s (1.111 ns period) as shown in the following figure. Because the system is double data rate, the interface operates at 1800 Mb/s.

The design is tested with the Vivado Simulator 2020.2. This section describes how to launch the simulation. Assuming the Vivado project is already created for the design, follow these steps to simulate the design.

-

Under Simulation Sources, right click toplevel_testbench_mb.sv and select Set as Top. Then, under Simulation from the Flow Navigator click Run Simulation.

-

From the listed options, select Run Behavioral Simulation, which elaborates the design and launches the simulation. Add desired signals such as intf_rdy, pll_locked, and int_prbs_err* to the waveform.

-

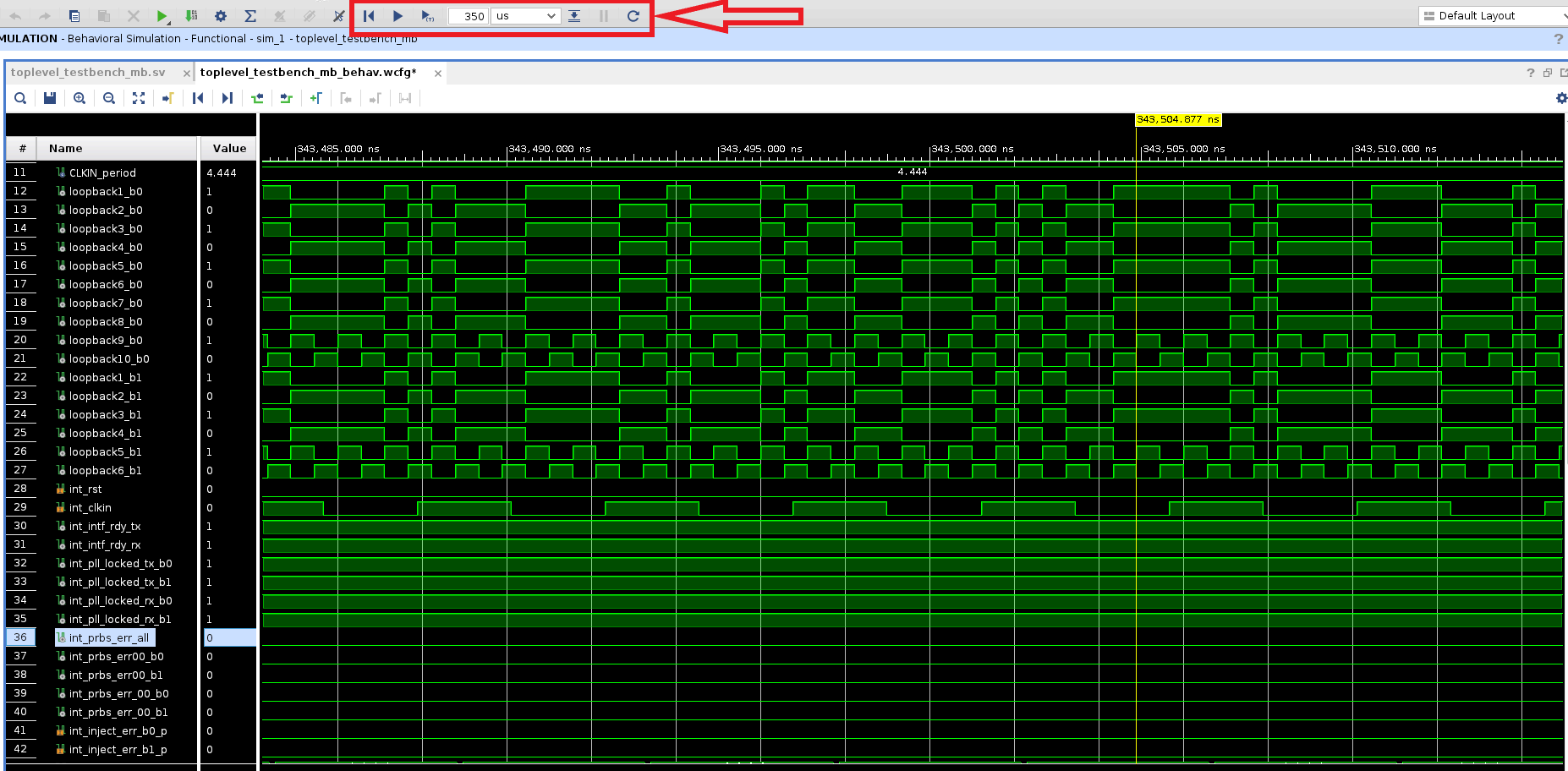

The run time for the simulation is 1 ns by default. It takes about 330 μs for the intf_rdy to be asserted for the RX core, which indicates that the Built In Self Calibration process has completed and the interface is ready for operation. Only after its assertion and the next Prbs_Valid should the data be compared. Consequently, launch the simulation for a duration of more than 330 μs using the box highlighted in the following figure. Add any additional signals if need be to the waveform.

- After the behavioral simulation is finished, check for any errors by observing error flags for the PRBS generator and checker. For example, int_prbs_err_b<0/1> reports the errors for each instantiation of the PRBS generator and checker. Int_prbs_err10_b0 denotes the error flag for the PRBS module instantiated for NIBBLE[1], NIBBLESLICE[0] of bank instance 0. Although the ports are named Tx_data_n0_bs2_p_b0, this does not necessarily mean that they would map to NIBBLE[0], NIBBLESLICE[2]. Refer to the schematics to check the exact mapping of any pin in the design. Int_prbs_err_00_b<0/1> denotes the error for any NIBBLESLICEs on NIBBLE[0]. Int_prbs_err_01_b<0/1> denotes the error for any NIBBLESLICEs on NIBBLE[0] and NIBBLE[1]. Int_prbs_err_all denotes an error on any NIBBLESLICE across all the nibbles in any of the bank instances.

Click to expand

This section describes the script to build the design using Versal_ssync_rxtx_intrfce_mb.tcl. This design was built on a machine with Linux OS. If running on Windows OS, there is a restriction with regard to the longest path. The user must make sure the project directory is located close to the C:/ drive (hierarchically, the project directory should be under the C:/ drive). Also, change the name of the directory Multi_bank_source_synchronous_design in this tutorial to a shorter name. Change the name of the variable xil_proj_name (variable that sets the name of the project) in the script to a shorter name. This script builds the design by adding all the source files, and adding and configuring the IP cores in the design. The script also launches the synthesis and implementation.

In order to run the script, make sure it is placed beside the Design, Constraints, and Simulation directories. Launch the Vivado tools, and in the TCL console, run the command: source ./Versal_ssync_rxtx_intrfce_mb.tcl.

It takes a few minutes for the script to build and implement the design.

Click to expand

This tutorial confirms the use of the Advanced I/O Wizard for a source synchronous application for multi-bank RX and TX interfaces.

Copyright © 2020–2024 Advanced Micro Devices, Inc.